AMD的3D V-Cache是透過3D封裝方式擴增L3快取容量,不過根據AMD專注研究快取架構的資深技術人員Carl Dietz發表的一篇「Balanced Latency Stacked Cache(平衡延遲堆疊快取)」的論文專利提到,AMD正探索透過3D封裝擴增L2快取並藉此實現更低的延遲。👀 pic.twittAMD的3D V-Cache是透過3D封裝方式擴增L3快取容量,不過根據AMD專注研究快取架構的資深技術人員Carl Dietz發表的一篇「Balanced Latency Stacked Cache(平衡延遲堆疊快取)」的論文專利提到,AMD正探索透過3D封裝擴增L2快取並藉此實現更低的延遲。👀 pic.twitt

AMD論文透露正探索透過3D封裝擴增L2快取容量並降低延遲

如需對本內容提供反饋或相關疑問,請通過郵箱 crypto.news@mexc.com 聯絡我們。

AMD的3D V-Cache是透過3D封裝方式擴增L3快取容量,不過根據AMD專注研究快取架構的資深技術人員Carl Dietz發表的一篇「Balanced Latency Stacked Cache(平衡延遲堆疊快取)」的論文專利提到,AMD正探索透過3D封裝擴增L2快取並藉此實現更低的延遲。

AMD已經證實透過3D封裝擴增L3快取能夠提升CPU的性能,然而由於L2快取對延遲要求相當高,路徑的長度變化都會影響延遲,故AMD發表的論文就相當有意思。在Carl Dietz論文的論述提到,透過3D封裝將L2快取進行堆疊,相對現行平面配置的快取約14個時脈週期的延遲,透過3D垂直封裝可縮減快取至CPU間的路徑,理論上可使快取延遲週期減少到12個時脈週期。

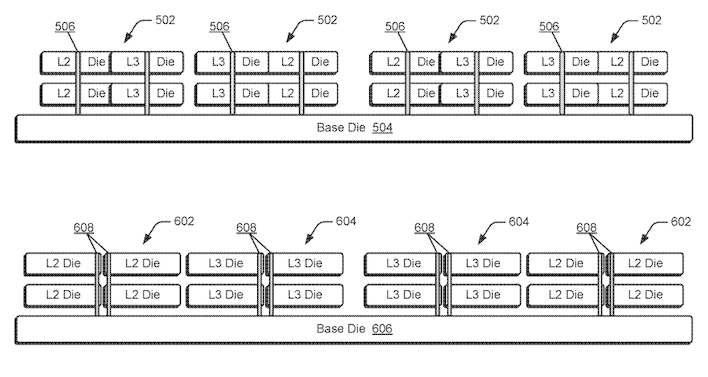

▲AMD的專利透露可在單一處理器封裝16個快取顆粒,且快取可為單一用於L2、L3、混合配置或共存

▲AMD的專利透露可在單一處理器封裝16個快取顆粒,且快取可為單一用於L2、L3、混合配置或共存

Carl Dietz還提到多種快取封裝方式,包括僅封裝L2快取,將同一個快取用於L2與L3,或獨立封裝用於L2及L3的快取,根據專利示意圖,AMD可在一個處理器透過3D封裝配置高達16個快取晶片。

但AMD最後會不會實作這項技術,仍舊取決於成本、良率、散熱與效益等條件,不過更大的L2快取當然是有助提升指令獲取的速度與降低L3快取負擔,而藉由3D封裝亦可實現比平面配置更大的快取容量,這也是這項技術的願景所在。

免責聲明: 本網站轉載的文章均來源於公開平台,僅供參考。這些文章不代表 MEXC 的觀點或意見。所有版權歸原作者所有。如果您認為任何轉載文章侵犯了第三方權利,請聯絡 crypto.news@mexc.com 以便將其刪除。MEXC 不對轉載文章的及時性、準確性或完整性作出任何陳述或保證,並且不對基於此類內容所採取的任何行動或決定承擔責任。轉載材料僅供參考,不構成任何商業、金融、法律和/或稅務決策的建議、認可或依據。

您可能也會喜歡

中國人民銀行美元/人民幣參考匯率調整:解讀6.8654的戰略性定盤價

本文《中國人民銀行美元/人民幣參考匯率調整:解讀策略性的 6.8654 定盤價》首次發表於 BitcoinEthereumNews.com。中國人民銀行美元/人民幣參考匯率調整

分享

BitcoinEthereumNews2026/04/10 11:17

值得關注的新加密貨幣:BlackRock BUIDL 擴張,Pepeto 預售快速完成

BlackRock 的代幣化美國國債基金 BUIDL 透過與 Securitize 合作在 Uniswap 上推出,將超過 20 億美元的真實世界資產放在去中心化

分享

Techbullion2026/04/10 11:20

Bittensor翻車?訓練團隊Covenant AI怒嗆「假的去中心化」宣告退出,TAO 跌超 17%

曾經被輝達執行長黃仁勳公開認可的去中心化 AI 訓練團隊 Covenant AI,正式宣布退出 Bittens […] 〈Bittensor翻車?訓練團隊Covenant AI怒嗆「假的去中心化」宣告退出,TAO 跌超 17%〉這篇文章最早發佈於動區BlockTempo《動區動趨-最具影響力的區塊鏈新聞媒體》。

分享

Blocktempo ZH2026/04/10 13:02